|

(495)510-98-15

|

|

Меню

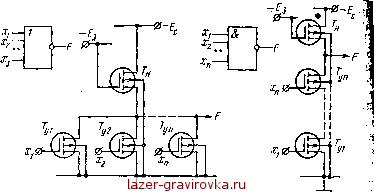

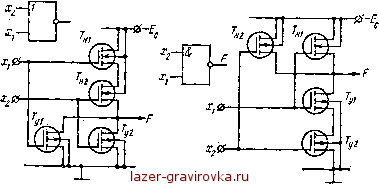

|

Главная » Промышленная электроника 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 [ 76 ] 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 Для отпирания транзистора к нему прикладывают напряжение ЩШ отрицательной полярности, превышающее Uao-p- ч9 Рассмотрим принцип действия схемы рис. 3.36, б. При х = 1 BJH ное напряжение (рис. 3.36, д) превышает пороговое и транзисторШ! открыт. Падение напряжения ЛсУои0 транзистора Ту мало. Тран1Я стор Тн также открыт, так как между его затвором и истоком пшИ кладывается напряжение Ес - Wcan, превышающее пороговое щй пряжение. Я Величина &Uca0, характеризующая состояние логического Я в схеме, определяется соотношением сопротивлений каналов RWt Rm проводящих транзисторов: Я А^сио = Ес (З.Щ Поскольку напряжение Ас/ио0 должно быть малым, необходим] чтобы RKyRm- Указанное условие выполняется благодаря осШ бенностям изготовления обоих транзисторов. Технологию микросхЦ мы выбирают так, чтобы получить в транзисторе Тн более узкий щ длинный канал, чем в транзисторе Тт Щ При х =- 0 (рис. 3.36, д) напряжение входного сигнала меньше ащ рогового напряжения с7ПОр транзистора TY и транзистор Гу закрыт! Через оба транзистора протекает небольшой ток, определяемый за! крытым транзистором Ту. При этом транзистор Т& работает на границе его отпирания с напряжением £/зи == cVnop. Логической 1 на выходё схемы соответствует напряжение Uca3 транзистора Ту, равное Ес -4 - Uuop. Если бы транзистор Тв был также закрыт, то ввиду большего5 сопротивления его канала логическая 1 характеризовалась бы малым выходным напряжением. Таким образом, особенность рассмотренной схемы заключается в том, что при ее переходе из режима логического О в режим логической 1 транзистор Тн переходит из открытого в предзакрытое Ц состояние. Схема рис. 3.36, в представляет собой улучшенный вариант предыдущей схемы. Усовершенствование направлено на повышение уровня напряжения логической 1 до значения, близкого к -Ес. Задача решается подключением затвора транзистора Тн к дополнительному источнику питания £8>Е0, благодаря чему открытое со- стояние транзистора Та распространяется и на режим логической Ь. ; Как и в предыдущей схеме, уровень логического О определяется \ различием в сопротивлениях каналов проводящих транзисторов. В режиме логической 1 транзистор Ту закрыт, а транзистор Т н крыт, поскольку напряжение Еа на его затворе превышает по абсолютному значению напряжение стока Е0 на величину, большую порогового напряжения транзистора ТИ (примерно на ту же величину напряжение на затворе будет превышать и напряжение истока транзистора 7\). Ток в цепи мал и определяется остаточным током закрытого транзистора Гу. Однако ввиду того что транзистор Г н открыт и сопротивление его канала мало, к транзистору Ту прикладывается напряжение, близкое к -£ . Обе рассмотренные схемы характеризуются потреблением тока от очника питания - Ес в режиме логического О (х = 1), так же йС3. и у элемента НЕ на биполярном транзисторе. Этим режимом, по К тпеству, и определяется мощность, потребляемая такими схемами в поонессе их работы. Потребляемую мощность можно сократить до минимума, если обес-ечить управление транзисторами Ту, Тн, при котором открытому со-т-оянию одного транзистора соответствует закрытое состояние другого. По такому принципу работает схема НЕ на дополняющих МДП - транзисторах (комплементарная МДП -стрУктУРа) (Рис- 3-36, г). В этой схеме в качестве Ту использован транзистор с каналом /7-типа, а в качестве Та - транзистор с каналом n-типа. При обратном сочетании транзисторов схема потребует напряжения питания положительной полярности. Принцип действия схемы на рис. 3.36, г заключается в следующем. При*= 1 транзистор Ту открыт, так как для него \U3a\ > £/пор|; транзистор Тн закрыт, поскольку для этого транзистора с7зи-< 0. Вследствие высокого сопротивления канала закрытого транзистора Тв и низкого сопротивления канала открытого транзистора Ту напряжение на выходе близко к нулю (F = 0). Ток, протекающий через структуру, достаточно мал. При х = 0 транзистор Ту закрыт, так как для него с7зи< <1п0р1 а транзистор Тн открыт, поскольку U3B > (7пор > 0. Сопротивление канала транзистора Ту велико, а сопротивление канала транзистора Тн мало, в связи с чем ток здесь также весьма мал, а выходное напряжение близко к -Ес (F = 1). Мощность, потребляемая схемой, не превышает единиц микроватт, причем ее рассчитывают, исходя не из статического режима работы, а из динамического. Это объясняется тем, что мощность потребляется схемой от источника главным образом на этапах ее переключения, g Логические элементы ИЛИ - НЕ, И - НЕ. Логический элемент ИЛИ - НЕ на МДП-транзисторах с однотипными каналами проводимости получают заменой в элементе НЕ (рис. 3.36, б) одного управляющего транзистора группой из п управляющих транзисторов (рис. 3.37, а). Число входов элемента определяется числом параллельно включенных транзисторов. Все транзисторы схемы создаются на общей полупроводниковой подложке с общим потенциалом. Общий вывод подложки объединяют о точкой земля схемы. При наличии логической 1 хотя бы на одном из входов схемы Рис. 3.37, а один из управляющих транзисторов открыт и на выходе присутствует логический 0 . Уровню логической Ь по входу и выходу соответствует потенциал, близкий к -Ес, превышающий пороговое напряжение транзисторов; уровню логического 0 - потенциал, близкий к нулю, меньший (7пор. Схема элемента И - НЕ на однотипных МДП-транзисторах показана на рис. 3.37, б. Она содержит общий нагрузочный транзистор а и группу из п последовательно включенных управляющих тран- зисторов. На выходе схемы будет действовать сигнал логическ только при всех одновременно открытых управляющих транз-(Xj = %ч - - хп - [). Схемы элементов ИЛИ - НЕ, И - НЕ на дополняющих1 транзисторах (комплементарных МДП-структурах) получают последовательного соединения группы транзисторов одного  Рис. 3.37. Схемы логических элементов ИЛИ - НЕ (а) и И - НЕ (б) на однотипных МДП-транзисторах .-.2: параллельного соединения группы транзисторов другого т (рис. 3.38, а, б). Тем самым сохраняется описанная специфика pa6q транзисторов в элементарной комплементарной МДП-структу В схеме логического элемента ИЛИ - НЕ (рис. 3.38, а) после. вательно соединяют нагрузочные, а параллельно - управляю транзисторы. Управляющие транзисторы образуют нижнее пле  Рис. 3.38. Схемы логических элементов ИЛИ - НЕ (а) и И - НЕ (б) на дополняющих МДП-транзнсторах |

|

© 2025 ООО "Стрим-Лазер": Лазерная гравировка.

Все права нотариально заверены. Копирование запрещено. |